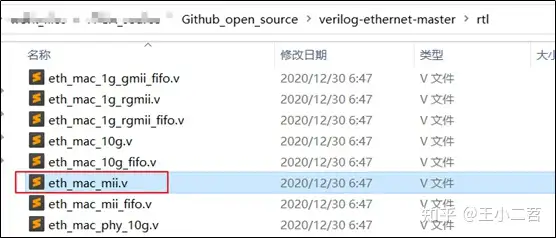

GitHub - MEEPproject/10gb_ethernet: 10Gb Ethernet solution shell compatible based on A.Forencich verilog-ethernet

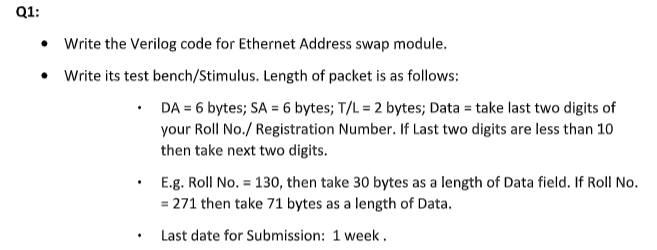

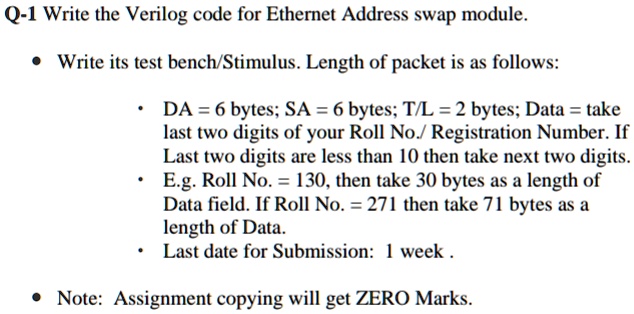

SOLVED: Write the Verilog code for an Ethernet Address swap module. Write its test bench/stimulus. The length of the packet is as follows: DA = 6 bytes; SA = 6 bytes; TIL =